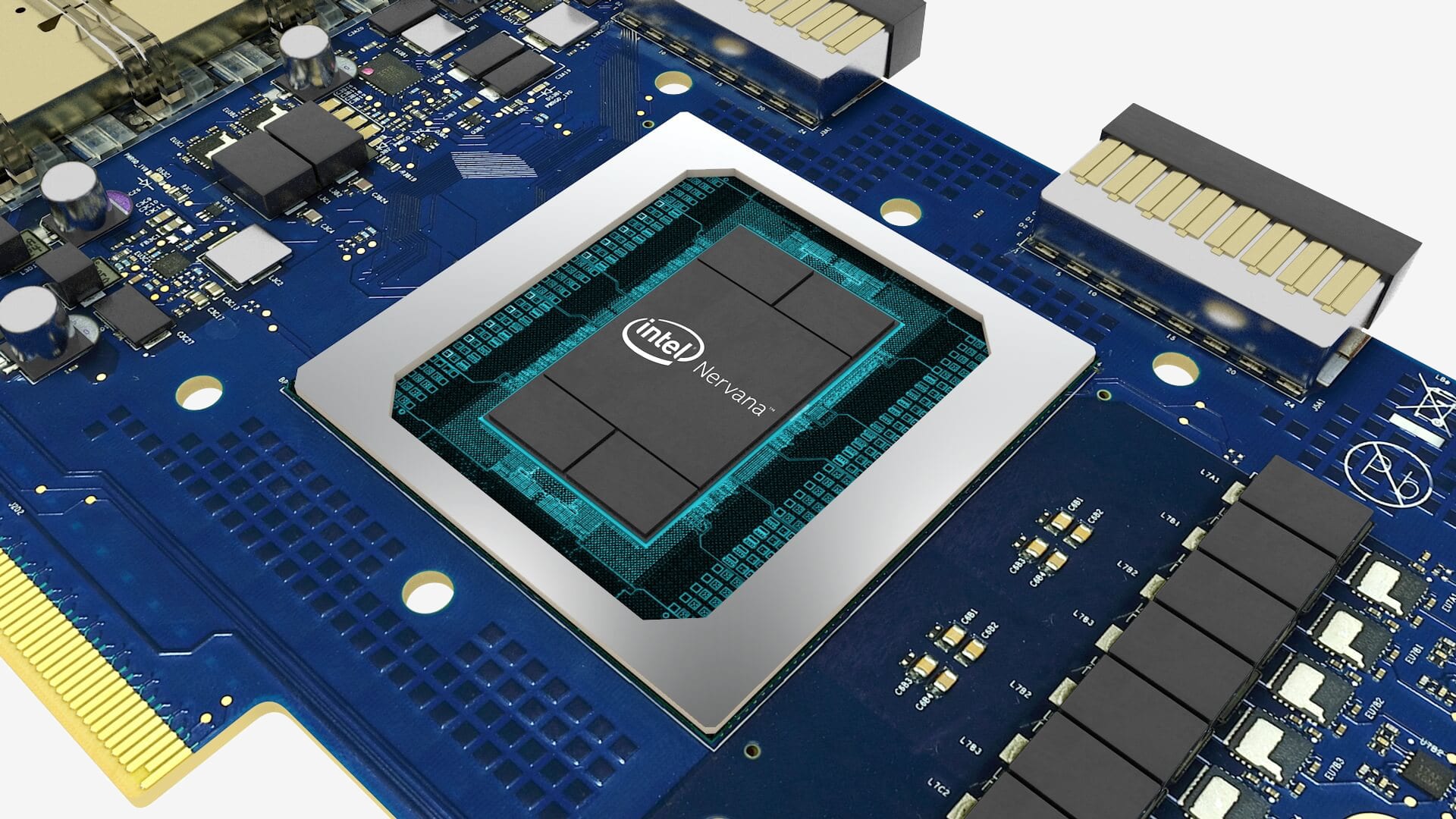

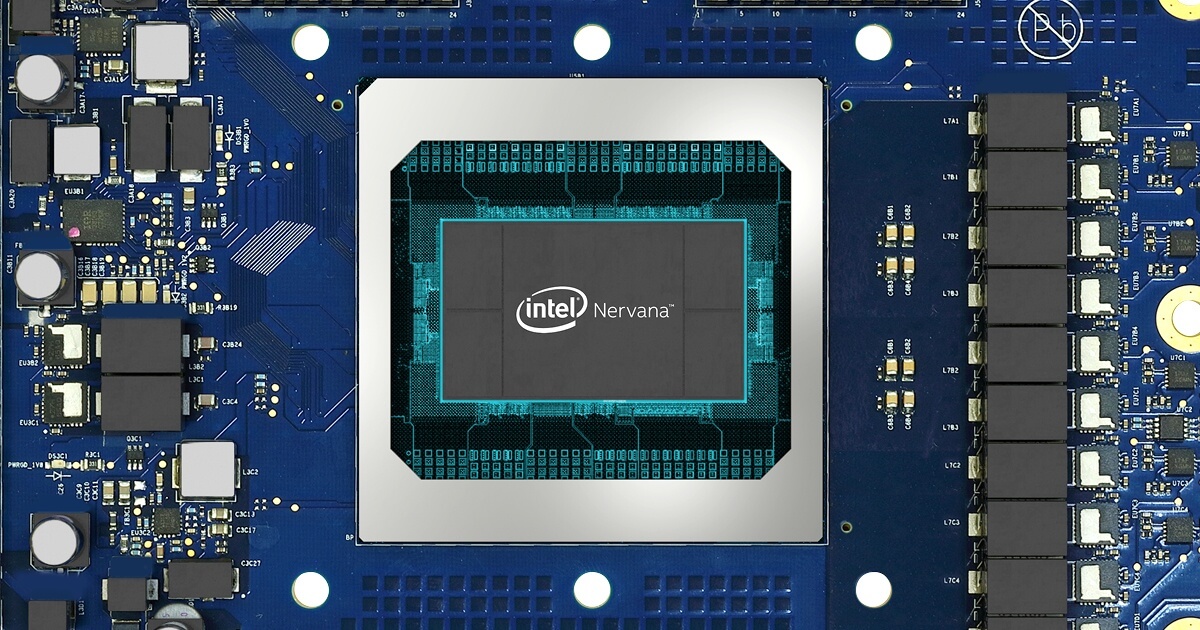

Hoy os queríamos hablar de los nuevos procesadores desarrollados por Intel para el campo de la Inteligencia Artificial, los nuevos Intel Nervana.

Lo nuevo en inteligencia artificial: Procesador Intel Nervana

Carey Kloss, vicepresidenta de hardware del grupo de productos de inteligencia artificial de Intel, ha dado una actualización sobre los refinamientos realizados a la arquitectura Nervana. Lo primero es entender los requisitos de lo que debe hacer un procesador de red neuronal (NNP). El entrenamiento de una máquina usando una red neuronal requiere cantidades masivas de operaciones aritméticas y de memoria para generar resultados útiles. Las capacidades de escalamiento, el consumo de energía y la máxima utilización son las consideraciones principales para la arquitectura espacial de Nervana. Para lograr el máximo ahorro de energía, los datos no deben moverse dentro del sistema a menos que sea absolutamente necesario. Los datos vectoriales se pueden dividir entre módulos de memoria para que los datos necesarios estén siempre cerca del lugar donde se necesiten.

Con la implementación de una memoria de un potente ancho de banda (HBM), es posible que el ancho de banda supere los 1TB/s entre los bancos de memoria externos y en la matriz. Aunque se trata de una cifra impresionante, el ancho de banda de la memoria sigue siendo un factor limitante para las cargas de trabajo de aprendizaje profundo. Como Intel no puede esperar a que se desarrollen nuevas tecnologías de memoria, se han desarrollado otras opciones creativas.

El control por software del uso de la memoria permite que la memoria en la matriz cargue la información de la memoria externa una vez y luego cambie los datos entre módulos de memoria local. Cada módulo es de aproximadamente 2MB con un total de unos 30MB por chip Nervana. La reducción de las lecturas a la memoria externa ayuda a evitar la saturación del ancho de banda de la memoria y permite preajustar el siguiente conjunto de datos necesario para el funcionamiento.

Una actualización al tipo de datos Flexpoint permite un rendimiento similar a las operaciones de punto flotante de 32 bits utilizando sólo 16 bits de almacenamiento. Utilizando la mitad del número de bits, el ancho de banda de memoria disponible se duplica efectivamente. Flexpoint es también modular para que las futuras generaciones de Nervana puedan reducir aún más el número de bits que requiere Flexpoint.

La comunicación entre el chip y los componentes externos se ha mejorado significativamente para ofrecer un rendimiento bidireccional de clase terabit. Un clúster de chips Nervana puede trabajar en una sola tarea como si el clúster fuera un único procesador masivo debido a la comunicación de alta velocidad entre los chips.